一、模块申明

verilog HDL设计以模块为基础,以关键字module开始,以endmodule结束,其格式如下:

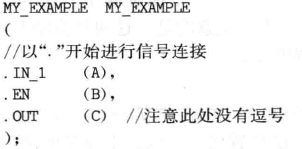

二、模块例化

对于模块例化(实例调用)的时候,需要将两个端口的信号连接起来,在Verilog HDL中有两种方法进行端口连接:顺序连接和名称连接。这两种连接方式只可单独使用,不可混合使用。

1.顺序连接

需要连接到模块实例的信号必须和模块声明时的目标端口列表中的位置保持一致。

2.名称连接法

顺序连接法只实用在端口较少的简单设计中,与其需要保证端口列表顺序有关,常用的连接方法是名称连接法。名称连接法中端口和像一个的外部信号按照其名字进行连接